Lesson 7Functinal Description of 8085

Elenco ElectronicsМвЄЮЅГЅѓЅдЅхЁМЅПЁМЅШЅьЁМЅЫЅѓЅАЅмЁМЅЩ MICRO-MASTER MM-8000 ЄЮ Lesson 7 ЄЫДиЄЙЄыЅсЅтЄЧЄЙЁЅЄГЄГЄЧЄЯЁЄМчЄЫIntelМвЄЮMPU 8085ЄЮЅЯЁМЅЩЅІЅЇЅЂЁМЙНРЎЄЫЄФЄЄЄЦГиНЌЄЗЄоЄЙ(ЛВОШЁЇMM=8000ЄЮЅоЅЫЅхЅЂЅыЄЮLesson 7)ЁЅ8085ЄЮЬПЮсЄЯЁЄМЁЄЮLesson 8ЄЧРтЬРЄЗЄоЄЙЁЅ

|

| 8085MPU(NEC 8442HD D8085AC) |

ЬмМЁ

1970ЧЏТхЄЮОѕЖЗ

ЮђЛЫ

8ЅгЅУЅШMPUЄЌМЁЁЙЄШГЋШЏЄЕЄьЄП1970ЧЏТхУцКЂЄоЄЧЄЮЮђЛЫЄђПЖЄъЪжЄУЄЦЄпЄоЄЗЄчЄІЁЅIntelМвЄЮКЧНщЄЮMPUЄЧЄЂЄы4004ЄЌДАРЎЄЗЄПЄЮЄЯ1971ЧЏЄГЄШЄЧЄЙЁЅЄГЄьЄЯЁЄ4ЅгЅУЅШЄЮMPUЄЧХіНщЄЯХХТюЭбЄЫГЋШЏЄЕЄьЄоЄЗЄПЁЅМЁЄЫЁЄ8ЅгЅУЅШЄЮMPU 8008ЄЌ1972ЧЏЄЫДАРЎЄЗЄоЄЙЁЅЄГЄьЄЯЭбХгЄЌРЉИТЄЕЄьЄПЄПЄсЁЄЄЂЄоЄъЩсЕкЄЗЄоЄЛЄѓЄЧЄЗЄПЁЅЬЕЭ§ЄЫ18ЅдЅѓЄЮЅбЅУЅБЁМЅИЄЫЕЭЄсЙўЄѓЄРЄГЄШЄЌТчЄЄЪЬфТъЄРЄУЄПЄшЄІЄЧЄЙЁЅЄНЄГЄЧЁЄТчЩ§ЄЫВўЮЩВУЄЈЄщЄьЄП40ЅдЅѓЄЮ8080ЄЌ1974ЧЏЄЫХаОьЄЗЄоЄЙЁЅЄГЄЮ8080ЄЯ80ЗЯЄЮИЕСФЄШЄЄЄяЄьЄыCPUЄЧЁЄ8085ЁЄZ80ЄиЄФЄЪЄЌЄъЄоЄЙЁЅЄГЄЮ8080ЄЯЁЄРЄГІНщЄЮЅбЁМЅНЅЪЅыЅГЅѓЅдЅхЁМЅПЁМЄЧЄЂЄыMITSМвЄЮAltair 8800ЄђРИЄрЄяЄБЄЧЁЄЄНЄЮИхЄЮPCЄЮШЏХИЄЫТчЄЄЪДѓЭПЄђВЬЄПЄЗЄПЄШЛзЄЄЄоЄЙЁЅЄПЄРЁЄ8080ЄЫЄтХХИЛЄЮЬфТъ(±5ЄШ12VЄЌЩЌЭз)ЄЪЄЩЄЌЄЂЄъЁЄ8085ЄЯЄНЄьЄщЄђВђЗшЄЗЄоЄЗЄПЁЅ8085ЄЮЅоЅЄЅЪЁМЄЪЅаЁМЅИЅчЅѓЅЂЅУЅзЄЗЄПЄтЄЮЄЌЄГЄГЄЧЛШЄІ8085AЄЧЄЙЁЅЄНЄЮИхЁЄ8ЅгЅУЅШMPUЄЮОЁМдЄЧЄЂЄыZilogМвЄЮZ80ЄЌШЏЧфЄЕЄьЄПЄЮЄЌ1976ЧЏЄЧЄЙЁЅ

ЄГЄГЄЧЄЮКюЄыMM-8000ЄЯЁЄ1970ЧЏТхШОЄаЄЮЅЂЅоЅСЅхЅЂЄЌКюЄУЄЦЄЄЄПЅГЅѓЅдЅхЁМЅПЁМЄШЛїЄЦЄЄЄоЄЙЁЅЩсФЬЄЮЅЂЅоЅСЅхЅЂЄЌКюЄьЄыЅбЁМЅНЅЪЅыЅГЅѓЅдЅхЁМЅПЁМЄЮИТГІЄЯЁЄ8ЅгЅУЅШЄЮMPUЄђЛШЄУЄПЄтЄЮЄЧЄЗЄчЄІЁЅЩєЩЪХРПєЄЯОЏЄЪЄЄЄЗЁЄЄНЄЮЦАКюЄтУБНуЄРЄЋЄщЄЧЄЙЁЅЄНЄЮЄПЄсЁЄЁжГиНЌЖЕКрЄЫКЧХЌЁзЄШЛзЄІЄЮЄЯЛфЄРЄБЄЧЄЯЄЪЄЄЄЯЄКЄЧЄЙЁЅИНКпЄЮ64/32ЅгЅУЅШЄЮЅбЁМЅНЅЪЅыЅГЅѓЅдЅхЁМЅПЁМЄЧЄтЁЄЄНЄЮД№ЫмЄЯТчЄЄЏЪбЄяЄУЄПЄяЄБЄЧЄЯЄЂЄъЄоЄЛЄѓЄЮЄЧЁЄДЪУБЄЪЖЕКрЄЧД№СУЄђГиНЌЄЙЄыЄГЄШЄЯТчЄЄЪАеЬЃЄЌЄЂЄъЄоЄЙЁЅ

ЄНЄЮТОЄЮMPUЄЫЄФЄЄЄЦЄтЁЄДЪУБЄЫЯУЄЗЄЦЄЊЄЄЄПЪ§ЄЌЮЩЄЄЄЧЄЗЄчЄІЁЅ8ЅгЅУЅШMPUЄЫЄЯЁЄ80ЗЯАЪГАЄЮ68ЗЯЄф65ЗЯЄЌЄЂЄъЄоЄЙЁЅ68ЗЯЄЮКЧНщЄЮMPUЄЯЁЄMC6800ЄЧ8080ЄЫПєЅіЗюУйЄьЄЦШЏЧфЄЕЄьЄПЄШЄЮЄГЄШЄЧЄЙЁЅЅпЅЫЅГЅѓЄЮPDP-11ЄЮЅЂЁМЅЅЦЅЏЅСЅуЁМЄђЛВЙЭЄЫРпЗзЄЗЄПЄШИРЄяЄьЄЦЄЄЄоЄЙЁЅ65ЗЯЄЯЁЄMOS TechnologyМвЄЮMOD 6502ЄШЄЄЄІMPUЄЌ1976ЧЏЄЫШЏЧфЄЕЄьЄоЄЗЄПЁЅЄГЄьЄЯЁЄВСГЪЄЌАТЄЋЄУЄПЄГЄШЄЋЄщЁЄApple IIЄЫХыКмЄЕЄьЁЄАьЬіЅсЅИЅуЁМЄЫЄЪЄъЄоЄЗЄПЁЅ

8085AЄШЄЯ

8085AЄЯЁЄ8ЅгЅУЅШЄЮШЦЭбMPUЄЧЄЙЁЅЦАКюЄЕЄЛЄыЄПЄсЄЮГАЩеЄБЩєЩЪЄЌОЏЄЪЄЄЄЮЄЧЁЄОЎЄЕЄЪЅЗЅЙЅЦЅрЄЧЄЯТчЪбЅГЅЙЅШЅбЅеЅЉЁМЅоЅѓЅЙЄЌЮЩЄЋЄУЄПЄшЄІЄЧЄЙЁЅ64KЅаЅЄЅШЄЮЅсЅтЅъЁМЄЌЛШЄЈЁЄЄоЄПТчЄЄЪЅЗЅЙЅЦЅрЄђРЉИцЄЙЄыЄПЄсЄЮЅЙЅЦЁМЅПЅЙЅщЅЄЅѓЄЌЄЂЄъЄоЄЙЁЅ

8085AЄЮЕЁЧН

8085AЄЮЦтЩєЙНТЄ

8085AЄЮОмКйО№ЪѓЄЌЩЌЭзЄЧЄЂЄьЄаЁЄЄЄЄэЄЄЄэЄЪWEBЅЕЅЄЅШЄЋЄщЅЧЁМЅПЅЗЁМЅШЄЌЅРЅІЅѓЅэЁМЅЩЄЧЄЄоЄЙЁЅЛфЄЯЁЄOKIЅЛЅпЅГЅѓЅРЅЏЅПГєМАВёМвЄЮЁжMSM80C85AHRS/GS/JSЄЮЅЧЁМЅПЅЗЁМЅШЁзЄђЛВЙЭЄЫЄЗЄоЄЗЄПЁЅ

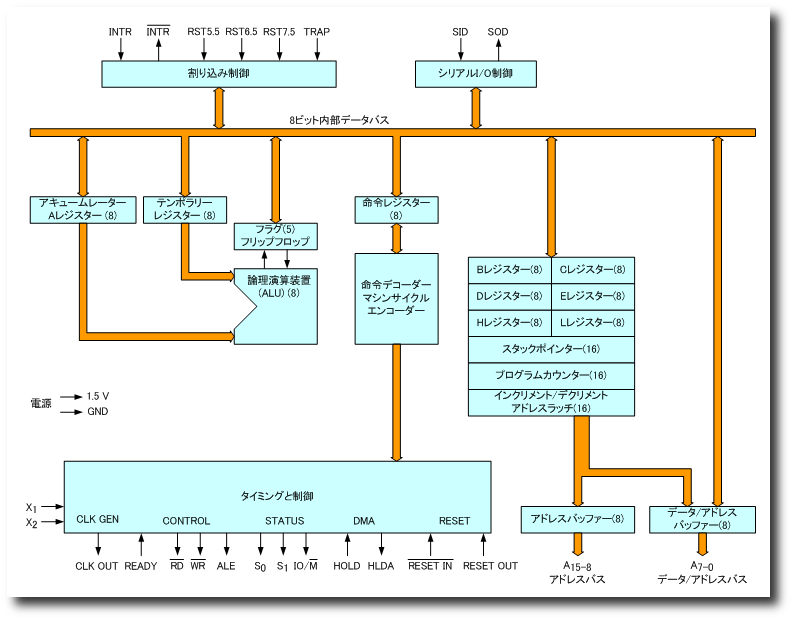

АЪВМЄЯЁЄЄлЄШЄѓЄЩЅоЅЫЅхЅЂЅы(WHAT'S IN THE 8085A)ЄЮЬѕЄЧЄЙЁЅ

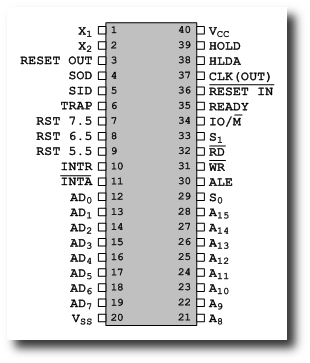

8085AЄЫЄЯЁЄЫмЭшЄЮMPUЄЮЬђГфЄЧЄЂЄыЬПЮсЅЛЅУЅШЄЮМТЙдЄЫВУЄЈЄЦЁЄЅЏЅэЅУЅЏШЏРИЄШЅЗЅЙЅЦЅрЅаЅЙРЉИцЁЄГфЄъЙўЄпЕЁЧНЄЌЄЂЄъЄоЄЙ(ВМПоЄЮЅжЅэЅУЅЏЅРЅЄЅЂЅАЅщЅрЄђЛВОШ)ЁЅ8085AЄЮЅЧЁМЅПХОСїЄЯЁЄ8ЅгЅУЅШУБАЬЄЧЙдЄяЄьЁЄСаЪ§ИўЄЮ3ЅЙЅЦЁМЅШЅаЅЙ(AD0ЁСAD7ЄЌЛШЄяЄьЄоЄЙЁЅЄГЄЮЅаЅЙЄЯЛўДжЪЌГфЄЕЄьЁЄЅЂЅЩЅьЅЙЄЮВМАЬ8ЅгЅУЅШЄЮХОСїЄЫЄтЛШЄяЄьЄоЄЙЁЅMPUЄЌФОРм64KЅаЅЄЅШЄЮЅсЅтЅъЁМЄЫЅЂЅЏЅЛЅЙЄЙЄыЄПЄсЄЫЄЯЁЄ16ЅгЅУЅШЄЮЅЂЅЩЅьЅЙЛиФъЄЌЩЌЭзЄЧЄЙЁЅЛФЄъЄЮОхАЬЄЮ8ЅгЅУЅШЄЮЛиФъЄЫЄЯЁЄAD8ЁСAD15ЄЌЛШЄяЄьЄоЄЙЁЅ8085AЄЯЁЄХЌХіЄЪГАЩєЅЧЅаЅЄЅЙЄђСЊТђЄШЁжЦЩЄпЙўЄпЁзЄШЁжНёЄЙўЄпЁзЄЮЦАКюЄЮМТЙдЁЄЅсЅтЅъЁМЄШI/OЅнЁМЅШЄЮСЊТђЄЮЄПЄсЄЮРЉИцПЎЙцЄђШЏРИЄЗЄоЄЙЁЅ8085AЄЫЄЯ256ЄЮI/OЭбЄЮЅЂЅЩЅьЅЙЄЌЄЂЄъЄоЄЙЁЅЄГЄьЄщЄЮЅЂЅЩЅьЅЙ(00HЁСFFH)ЄЯЁЄЅсЅтЅъЁМЄЮКЧНщЄЮ256ЄЮЅЂЅЩЅьЅЙЄШЦБАьЄЧЄЙЁЅЄГЄьЄЯЁЄ8085AЄЮIO/MЅдЅѓЄЮНаЮЯЄЧЖшЪЬЄЧЄЄоЄЙЁЅI/OЅнЁМЅШЄЯЁЄЅсЅтЅъЁМЄШЦБЄИЄшЄІЄЫАЗЄІЄГЄШЄЌЄЧЄЄоЄЙЁЅ

|

| 8085ЄЮЅжЅэЅУЅЏЅРЅЄЅЂЅАЅщЅр |

ЅьЅИЅЙЅПЁМ

ЅьЅИЅЙЅПЁМЄЯЁЄMPU ЄЮУцЄЫЄЂЄыЕВБОьНъЄпЄПЄЄЄЪЄтЄЮЄЧЄЙЁЅ8085 ЄЫЄЯЁЄ8 ЅгЅУЅШЄШ 16 ЅгЅУЅШЄЮЅьЅИЅЙЅПЁМЄЌЄЂЄъЄоЄЙ (По3)ЁЅ8 ЅгЅУЅШЄЮЅьЅИЅЙЅПЁМЄЯ 8 ИФ(A, B, C, D, E, H, L, ЅеЅщЅА)ЄЂЄъЁЄЄНЄЮЄІЄС 6 ИФЄЯЅьЅИЅЙЅПЁМЅкЅЂЄШЄЗЄЦЛШЄІЄГЄШЄЌЄЧЄЄоЄЙЁЅЅьЅИЅЙЅПЁМЅкЅЂ (BC, DE, HL) ЄЯЁЄ16 ЅгЅУЅШЄЮЅьЅИЅЙЅПЁМЄШЄЗЄЦЛШЄІЄГЄШЄЌЄЧЄЄоЄЙЁЅЄГЄьЄщЄЮЅьЅИЅЙЅПЁМЅкЅЂЄЫВУЄЈЄЦЁЄ8085A ЄЯ 2 ИФЄЮ 16 ЅгЅУЅШЅьЅИЅЙЅПЁМ (ЅЙЅПЅУЅЏЅнЅЄЅѓЅПЁМ, ЅзЅэЅАЅщЅрЅЋЅІЅѓЅПЁМ) ЄЌЄЂЄъЄоЄЙЁЅ

|

| 8085ЄЮЅьЅИЅЙЅПЁМЙНРЎ |

ЅЂЅЅхЅрЅьЁМЅПЁМ (ACC ЄЂЄыЄЄЄЯAЅьЅИЅЙЅПЁМ) ЄЯ,ЛЛНбБщЛЛЄфЯРЭ§БщЛЛЁЄЅЧЁМЅПЄЮХОСїЁЄI/O ЄЮЬПЮсЄЧЛШЄяЄьЄоЄЙЁЅШЦЭбЅьЅИЅЙЅПЁМЄШИЦЄаЄьЄыЄГЄШЄтЄЂЄъЄоЄЙЁЅ

ЅзЅэЅАЅщЅрЅЋЅІЅѓЅПЁМ (PC) ЄЯЁЄМЁЄЫМТЙдЄЙЄыЬПЮсЄЌГЪЧМЄЕЄьЄЦЄЄЄыЅсЅтЅъЁМЄЮЅЂЅЩЅьЅЙЄђЪнЛ§ЄЗЄоЄЙЁЅ8085A ЄЮЅсЅтЅъЁМЅЂЅЩЅьЅЙЄЗЄЦЄЯ16ЅгЅУЅШЄЪЄЮЄЧЁЄЅзЅэЅАЅщЅрЅЋЅІЅѓЅПЁМЄт 16 ЅгЅУЅШЄЧЄЙЁЅ

BC ЄШ DEЁЄHL ЄЯШЦЭбЅьЅИЅЙЅПЁМЄЧЁЄЬПЮсЄЫЄшЄъ 8 ЅгЅУЅШЅьЅИЅЙЅПЁМЄЂЄыЄЄЄЯ 16 ЅгЅУЅШЄЮЅьЅИЅЙЅПЁМЄЫЄЪЄъЄоЄЙЁЅHL ЅьЅИЅЙЅПЁМЄЯЁЄЬПЮсЄЮСрКюТаОнЄЮЅНЁМЅЙ(ИЕ)ЄфЅЧЅЙЅЦЅЃЅЭЁМЅЗЅчЅѓ(ЬмХЊ)ЄЮЅсЅтЅъЄЮЅЂЅЩЅьЅЙЄђЩНЄЙЅЧЁМЅПЅнЅЄЅѓЅПЁМЄШЄЗЄЦЛШЄяЄьЄоЄЙ(ЖёТЮХЊЄЫЄЯЁЄLesson 8 ЄЮ HL ЅьЅИЅЙЅПЁМЄђЛШЄУЄЦЄЄЄыЬПЮсЄђЛВОШЄЗЄЦЄЏЄРЄЕЄЄ)ЁЅОЏЄЪЄЄЄЧЄЙЄЌЁЄBC ЄЂЄыЄЄЄЯ DE ЅьЅИЅЙЅПЁМЄђДжРмЅЂЅЩЅьЅУЅЗЅѓЅАЄЫЛШЄІЬПЮсЄтЄЂЄъЄоЄЙЁЅ

ЅЙЅПЅУЅЏЅнЅЄЅѓЅПЁМ (SP) ЄЯЁЄЅЙЅПЅУЅЏЄЮЅШЅУЅз (МЁЄЫЭјЭбВФЧНЄЪЅЙЅПЅУЅЏЄЮЅЂЅЩЅьЅЙ) ЄђМЈЄЙЦУЪЬЄЪЅЧЁМЅПЅнЅЄЅѓЅПЁМЄЧЄЙЁЅ16 ЅгЅУЅШЄЮЅьЅИЅЙЅПЁМЄЧ8ЅгЅУЅШЄЫЪЌГфЄЙЄыЄГЄШЄЯЄЧЄЄоЄЛЄѓЁЅЅЂЅЩЅьЅЙЄђЩНЄЙЄПЄсЁЄЩЌЄК 16 ЅгЅУЅШЩЌЭзЄРЄЋЄщЄЧЄЙЁЅ

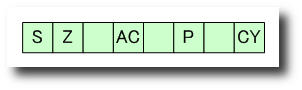

8 ЅгЅУЅШЄЮЅеЅщЅАЅьЅИЅЙЅПЁМЄЫЄЯЁЄ5 ЄФЄЮ 1 ЅгЅУЅШЄЮЅеЅщЅАЄЌДоЄоЄьЄЦЄЄЄоЄЙЁЅЄГЄьЄщЄЮЅеЅщЅАЄЯЁЄMPU ЄЮОѕТжЄђЩНЄЗЁЄMPU ЄЮЦАКюЄђРЉИцЄЗЄоЄЙЁЅ

ЅеЅщЅАЅьЅИЅЙЅПЁМ

По4ЄЫЁЄ8085ЄЮЅеЅщЅАЅьЅИЅЙЅПЁМЄЮЙНРЎЄђМЈЄЗЄоЄЙЁЅ

|

| ЅеЅщЅАЅьЅИЅЙЅПЁМ |

ЗхОхЄВЅеЅщЅАCY(carry flag)ЄЯЁЄЛЛНбБщЛЛЬПЮсЄфЯРЭ§БщЛЛЬПЮсЄЮЗыВЬЄЫЄшЄУЄЦЁЄЅЛЅУЅШЄфЅъЅЛЅУЅШЄЕЄьЄоЄЙЁЅЄПЄШЄЈЄаЁЄМЁЄЮЄшЄІЄЪ1ЅаЅЄЅШЦБЛЮЄЮТЄЗЛЛЄЧЗхОхЄВЄЌРИЄИЄПОьЙчЄЫЁЄЗхОхЄВЅеЅщЅАCYЄЌЅЛЅУЅШ(1)ЄЕЄьЄоЄЙЁЅЄГЄЮЅеЅщЅАЄђЛШЄІЄГЄШЄЧЁЄБщЛЛЗыВЬЄЌ8ЅгЅУЅШЄЫМ§ЄоЄщЄЪЄЄВУЛЛЄЧЄтРЕЄЗЄЄЗыВЬЄђЦРЄыЄГЄШЄЌЄЧЄЄоЄЙЁЅ

10101110+ 01110100

100100010

ВУЛЛБщЛЛЄЮЗзЛЛЗыВЬЄЌ8ЅгЅУЅШЄЧЅЊЁМЅаЁМЅеЅэЁМЄЗЄПОьЙчЁЄЅЅуЅъЁМЅеЅщЅАЄЌЅЛЅУЅШ(CY=1)ЄЕЄьЄоЄЙЁЅЅЊЁМЅаЁМЅеЅэЁМЄЌЕЏЄЄЪЄЄОьЙчЄЫЄЯЁЄЅъЅЛЅУЅШ(CY=0)ЄЕЄьЄоЄЙЁЅИКЛЛБщЛЛЄЮОьЙчЄЫЄЯЁЄЅЅуЅъЁМЅеЅщЅАЄЯЁжОхАЬЄЮЗхЄЋЄщЄЮМкЄъ(ЅмЅэЁМ)ЁзЄЫЄЪЄъЄоЄЙЁЅВМЄЮКИТІЄЮЮуЄЯЁЄИКЛЛЄЕЄьЄыПє(10101110)ЄшЄъЄтИКЛЛПє(01110100)ЄЮЪ§ЄЌТчЄЄЄЄЮЄЧЁЄЁжОхАЬЄЮЗхЄЋЄщЄЮМкЄъЁзЄЯРИЄИЄоЄЛЄѓЄЮЄЧЁЄCY=0ЄШЄЪЄъЄоЄЙЁЅАьЪ§ЁЄБІТІЄЮЮуЄЧЄЯМкЄъ(РжЛњ)ЄЌРИЄИЄоЄЙЄЮЄЧЁЄCY=1ЄШЄЪЄъЄоЄЙЁЅ

10101110 101110100- 01110100 - 10101110

00111010 11000110

ACЅеЅщЅАЄЯЁЄЅгЅУЅШ3ЄЌЗхОхЄВЄфОхАЬЗхЄЋЄщЄЮМкЄъЄЌРИЄИЄПОьЙчЄЫЁЄЅЛЅУЅШ(AC=1)ЄЕЄьЄоЄЙЁЅЅЅуЅъЁМЅеЅщЅА(CY)ЄЌЅгЅУЅШ7ЄЧЦАКюЄЗЄПЄЮЄШЦБЄИЄГЄШЄЌЁЄЅгЅУЅШ3ЄЧЕЏЄЄоЄЙЁЅЄГЄЮACЅеЅщЅАЄЯЁЄ10ПЪПєБщЛЛЄЮЛўЄЫЛШЄЄЄоЄЙЁЅ

БщЛЛЗыВЬЄЮРЕЩщЄђЩНЄЙЅЕЅЄЅѓЅеЅщЅА (S) ЄЯЁЄЛЛНбБщЛЛЬПЮсЄфЯРЭ§БщЛЛЬПЮсЄЮМТЙдЗыВЬЄЌГЪЧМЄЕЄьЄыЅЂЅЅхЁМЅрЅьЁМЅПЁМ (AЅьЅИЅЙЅПЁМ) ЄЮКЧОхАЬЅгЅУЅШЄЌЅЛЅУЅШЄЕЄьЄоЄЙЁЅРАПєЄђ 2 ЄЮЪфПєЄЧЩНЄЙЅЗЅЙЅЦЅрЄЧЄЯЁЄКЧОхАЬЅгЅУЅШЄЌ 1 ЄЫЄЪЄыЄШЁЄЄНЄЮРАПєЄЯЩщЄШЄЗЄЦМшЄъАЗЄяЄьЄоЄЙЁЅЄЗЄПЄЌЄУЄЦЁЄЅЂЅЅхЁМЅрЅьЁМЅПЁМЄЮКЧОхАЬЅгЅУЅШЄђФДЄйЄыЄГЄШЄЧБщЛЛЗыВЬЄЮРЕЩщЄЌЪЌЄЋЄъЄоЄЙЁЅЅГЅѓЅдЅхЁМЅПЁМЦтЩєЄЧЄЮЩщЄЮРАПєЄЮЩНИНЄЫЄФЄЄЄЦЄЯЁЄЛфЄЮЙжЕСЅЮЁМЅШЁжЩщЄЮРАПєЄЮЩНИНЁзЄђЛВОШЄЏЄРЄЕЄЄЁЅ

ЅМЅэЅеЅщЅА (Z) ЄЯЁЄЅЂЅЅхЁМЅрЅьЁМЅПЁМ (AЅьЅИЅЙЅПЁМ) ЄЮСДЄЦЄЮЅгЅУЅШЄЌЅМЅэЄЮЛўЁЄЅЛЅУЅШ (Z=1) ЄЕЄьЄоЄЙЁЅШПТаЄЫЄЩЄьЄЋЄЮЅгЅУЅШЄЌ 1 ЄЮЛўЁЄЅЏЅъЅЂЁМ (Z=0) ЄЕЄьЄоЄЙЁЅ+1 ВУЛЛЬПЮс (INR) Єф -1 ИКЛЛЬПЮс (DCR) ЄЮЗыВЬЄЫЄтЁЄЅМЅэЅеЅщЅАЄЯШПБЧЄЕЄьЄоЄЙЁЅ

ЅЂЅЅхЁМЅрЅьЁМЅПЁМ (AЅьЅИЅЙЅПЁМ) ЄЮЅгЅУЅШЄЮ1ЄЮПєЄЌЖіПєЄЮОьЙчЁЄЅбЅъЅЦЅЃЅеЅщЅА (P) ЄЌЅЛЅУЅШ (P=1) ЄЕЄьЄоЄЙЁЅЖіПєЄЮОьЙчЁЄЅЏЅъЅЂЁМ (P=0) ЄЕЄьЄоЄЙЁЅ

ЅЙЅПЅУЅЏЅнЅЄЅѓЅПЁМ

ЅЙЅПЅУЅЏЅнЅЄЅѓЅПЁМЄЯЁЄЅЙЅПЅУЅЏЄЮКЧОхАЬЄЮЅЂЅЩЅьЅЙЄЌГЪЧМЄЕЄьЄоЄЙЁЅЅЙЅПЅУЅЏЄЯЁЄЅсЅтЅъЁМ(RAM)ЄЮАьЩєЄђЛШЄЄЁЄЅЧЁМЅПЄЮГЪЧМ(PUSH)ЄШЅЧЁМЅПЄђМшЄъНаЄЗ(POP)ЄђЙдЄЄЄоЄЙЁЅНщДќВНЛўЄЫЄЯЁЄЛШЭбВФЧНЄЪЅсЅтЅъЁМКЧТчЄЮШжУЯ(КЧВМАЬШжУЯ)ЄђЅЙЅПЅУЅЏЅнЅЄЅѓЅПЁМЄЮУЭЄШЄЗЄоЄЙЁЅЅЙЅПЅУЅЏЄЫЅЧЁМЅПЄЌЅзЅУЅЗЅх(PUSH)ЄЕЄьЄыЄШЅЙЅПЅУЅЏЅнЅЄЅѓЅПЁМЄЮУЭЄЯИКЄщЄЕЄьЁЄЅнЅУЅз(POP)ЄЕЄьЄыЄШС§ЄфЄЕЄьЄоЄЙ(ЅЙЅПЅУЅЏЄЯЁЄЅсЅтЅъЁМЄЮВМАЬЄЋЄщОхАЬЄЫИўЄЋЄУЄЦПЄгЄоЄЙ)ЁЅЅЙЅПЅУЅЏЄЫЄЯЁЄОяЄЫ2ЅаЅЄЅШЄКЄФЅЧЁМЅПЄЌГЪЧМЄЕЄьЄыЄЮЄЧЁЄЅЙЅПЅУЅЏЅнЅЄЅѓЅПЁМЄЯ2ЄКЄФС§ИКЄЗЄоЄЙЁЅ

БщЛЛЯРЭ§СѕУж(ALU)

ALUЄЫЄЯЁЄЅЂЅЅхЁМЅрЅьЁМЅПЁМЄфЅеЅщЅАЅьЅИЅЙЅПЁМЁЄЅзЅэЅАЅщЅоЁМЄЌЅЂЅЏЅЛЅЙЄЧЄЄЪЄЄЄЄЄЏЄФЄЋЄЮЅЦЅѓЅнЅщЅъЁМЄЪЅьЅИЅЙЅПЁМЄЌДоЄоЄьЄоЄЙЁЅЛЛНбБщЛЛЄфЯРЭ§БщЛЛЁЄЅэЁМЅЦЁМЅШБщЛЛЄЯЁЄALUЄЫЄшЄУЄЦМТЙдЄЕЄьЄоЄЙЁЅЄНЄьЄщЄЮБщЛЛЗыВЬЄЯЁЄЅЂЅЅхЁМЅрЅьЁМЅПЁМЄЫГЪЧМЄЕЄьЄыЄЋЁЄТОЄЮОьНъЄЧЛШЄІЄПЄсЄЫЦтЩєЄЮЅЧЁМЅПЅаЅЙЄЫСїЄщЄьЄоЄЙЁЅ

ЬПЮсЅьЅИЅЙЅПЁМЄШЅЧЅГЁМЅРЁМ

ЅеЅЇЅУЅСЅЕЅЄЅЏЅыЄЮДжЁЄЬПЮсЄЮКЧНщЄЮЅаЅЄЅШ(ЅЊЅкЅГЁМЅЩЄђДоЄѓЄЧЄЄЄы)ЄЯЁЄЦтЩєЅаЅЙЄђФЬЄЗЄЦ8ЅгЅУЅШЄЮЬПЮсЅьЅИЅЙЅПЁМЄЫСїЄщЄьЄоЄЙЁЅЄФЄЎЄЫЁЄЬПЮсЅьЅИЅЙЅПЁМЄЮЦтЭЦЄЯЬПЮсЅЧЅГЁМЅРЁМЄЌЛШЄЄЄоЄЙЁЅЅПЅЄЅпЅѓЅАПЎЙцЄЫЄшЄУЄЦШЏРИЄЕЄЛЄщЄьЄыЅЧЅГЁМЅРЁМЄЮНаЮЯЄЯЁЄЅьЅИЅЙЅПЁМЄШALUЄШЅЧЁМЅПЄШЅЂЅЩЅьЅЙЅаЅУЅеЅЁЁМЄђРЉИцЄЗЄоЄЙЁЅЬПЮсЅьЅГЁМЅРЁМЄШЦтЩєЅЏЅэЅУЅЏШЏРИДяЄЯЁЄЅЙЅЦЁМЅШЄШЅЙЅЦЁМЅШЄШЅоЅЗЅѓЅЕЅЄЅЏЅыЄЮЅПЅЄЅпЅѓЅАПЎЙцЄђШЏРИЄЗЄоЄЙЁЅ

ЅдЅѓЅЂЅЕЅЄЅѓ

|

| 8085ЄЮЅдЅѓ |

ВѓЯЉЄЮРтЬР

ЅЦЅЙЅШНчНј

ЅкЁМЅИКюРЎО№Ъѓ

ЛВЙЭЛёЮС

- OKIЅЛЅпЅГЅѓЅРЅЏЅПГєМАВёМвЄЮMSM80C85AHRS/GS/JSЄЮЅЧЁМЅПЅЗЁМЅШЁЅ8085ЄЮЅЧЁМЅПЅЗЁМЅШЄЄЄэЄЄЄэУЕЄЗЄоЄЗЄПЄЌЁЄOKIЄЮЄтЄЮЄЌЗыЙНОмЄЗЄЋЄУЄПЄЮЄЧЛВЙЭЄЫЄЗЄоЄЗЄПЁЅ

- ЮыЬкХЏКШУјЄЮЁжИХХЕХХЧОЪЊИьЁзЄЯТчЪбЛВЙЭЄЫЄЪЄъЄоЄЙЁЅ8085ЄЮОмЄЗЄЄРтЬРЄЌЄЂЄъЁЄЅЯЁМЅЩЄЋЄщЅНЅеЅШЄоЄЧЅоЅЄЅГЅѓЄЮКюЄъЪ§ЄЌЄЋЄЋЄьЄЦЄЄЄоЄЙЁЅ

ИХХЕХХЧОЪЊИьЁН8085,Z80,CP/M,ЅПЅЄЅЫЁМBASICЁФ

ЅщЅШЅыЅК 2006-07

ЧфЄъОхЄВЅщЅѓЅЅѓЅА : 134755

AmazonЄЧОмЄЗЄЏИЋЄы by G-Tools - UNIXЅЗЅЙЅЦЅр(LinuxЄтЦАКюВФ)ЄЧЦАКюЄЙЄы8085ЄЮЅЈЅпЅхЅьЁМЅПЁМ EZ8085ЁЅЦАКюЄђГЮЧЇЄЙЄыЄШЄЄЫЁЄЅЈЅпЅхЅьЁМЅПЁМЄЌЄЂЄьЄаТчЪбЪиЭјЄЧЄЙЁЅ

ЙЙПЗЭњЮђ

| 2010ЧЏ01Зю10Цќ | ЅкЁМЅИЄЮПЗЕЌКюРЎ |